6

FN4837.5

October 16, 2006

output voltage. As the internal soft-start voltage increases, the

pulse-width on the PHASE pin increases to reach its

steady-state duty cycle at time T2. At time T3, the 3.3V input

supply starts ramping up; as a result, V

OUT2

and V

OUT4

start

ramping up on the second attempt (approximately 3.25 SS

cycles wait), at time T4. During the interval between T4 and T5,

the linear controller error amplifiers references ramp to the final

value bringing all outputs within regulation limits.

Overcurrent Protection

All outputs are protected against excessive overcurrents.

The PWM controller uses the upper MOSFETs

on-resistance, r

DS(ON)

to monitor the current for protection

against shorted output. All linear controllers monitor their

respective FB pins for undervoltage events to protect against

excessive currents.

A sustained overload (undervoltage on linears or overcurrent

on the PWM) on any output results in an independent

shutdown of the respective output, followed by subsequent

individual re-start attempts performed at an interval equivalent

to 3 soft-start intervals. Figure 2 describes the protection

feature. At time T0, an overcurrent event sensed across the

switching regulators upper MOSFET (r

DS(ON)

sensing)

triggers a shutdown of the V

OUT1

output. As a result, its

internal soft-start initiates a number of soft-start cycles. After a

three-cycle wait, the fourth soft-start initiates a ramp-up

attempt of the failed output, at time T2, bringing the output in

regulation at time T4.

To exemplify an UV event on one of the linears, at time T1,

the clock regulator (V

OUT2

) is also subjected to an

overcurrent event, resulting in an UV condition. Similarly,

after three soft-start periods, the fourth cycle initiates a

ramp-up of this linear output at time T3. One soft-start period

after T3, the linear output is within regulation limits. UV

glitches less than 1祍 (typically) in duration are ignored.

As overcurrent protection is performed on the synchronous

switcher regulator on a cycle-by-cycle basis, OC monitoring

is active as long as the regulator is operational. Since the

overcurrent protection on the linear regulators is performed

through undervoltage monitoring at the feedback pins (FB2,

FB3, and FB4), this feature is activated approximately 25%

into the soft-start interval (see Figure 2).

A resistor (R

OCSET

) programs the overcurrent trip level for

the PWM converter. As shown in Figure 3, the internal

40礎 current sink (I

OCSET

) develops a voltage across

R

OCSET

(V

SET

) that is referenced to V

IN

. The DRIVE

signal enables the overcurrent comparator (OCC). When

the voltage across the upper MOSFET (V

DS(ON)

) exceeds

V

SET

, the overcurrent comparator trips to set the

overcurrent latch. Both V

SET

and V

DS(ON)

are referenced

to V

IN

and a small capacitor across R

OCSET

helps

V

OCSET

track the variations of V

IN

due to MOSFET

switching. The overcurrent function will trip at a peak

inductor current (I

PEAK)

determined by:

The OC trip point varies with MOSFETs r

DS(ON)

temperature variations. To avoid overcurrent tripping in the

normal operating load range, determine the R

OCSET

resistor from the equation above with:

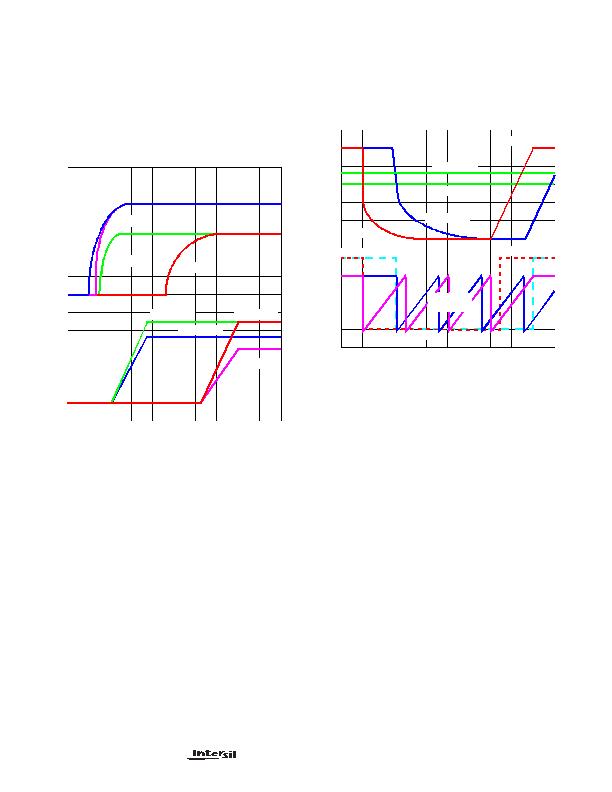

FIGURE 1. SOFT-START INTERVAL

0V

0V

TIME

+5V

SB

(0.5V/DIV)

V

OUT2

(2.5V)

V

OUT4

(1.5V)

T1

T2 T3

T0

T4

(1V/DIV)

+3.3V

IN

+5V

DUAL

+3.3V

DUAL

V

OUT3

(1.8V)

V

OUT1

(2.5V)

T5

FIGURE 2. OVERCURRENT/UNDERVOLTAGE PROTECTION

RESPONSE

0V

TIME

(0.5V/DIV.)

V

OUT3

(1.8V)

V

OUT2

(2.5V)

T1

T2

T3

T0

V

OUT4

(1.5V)

V

OUT1

(2.5V)

UV MONITORING

INACTIVE

SOFT-START

FUNCTION

ACTIVE

T4

I

PEAK

=

I

OCSET

R

OCSET

?/DIV>

r

DS ON

( )

--------------------------------------------------- -

HIP6521

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HMC920LP5E

IC CTRLR ACTIVE BIAS 32QFN

IDTTSE2002B3CNRG

IC TEMP SENS EEPROM DFN-8

IPM6220ACAZ-T

IC REG 5OUT BUCK/LDO SYNC 24SSOP

IR2170

IC CURRENT SENSE 600V 1MA 8-DIP

IR2171STR

IC CURRENT SENSE 8SOIC

IR2172S

IC CURRENT SENSE 8SOIC

IR2175STR

IC CURRENT SENSE 0.5% 8SOIC

IR22771STRPBF

IC CURRENT SENSE 16SOIC

相关代理商/技术参数

HIP6521CBZ

功能描述:电压模式 PWM 控制器 4 IN 1 PWM/LINEAR CNTRLR 5V RoHS:否 制造商:Texas Instruments 输出端数量:1 拓扑结构:Buck 输出电压:34 V 输出电流: 开关频率: 工作电源电压:4.5 V to 5.5 V 电源电流:600 uA 最大工作温度:+ 125 C 最小工作温度:- 40 C 封装 / 箱体:WSON-8 封装:Reel

HIP6521CBZA

功能描述:IC REG QD BCK/LINEAR 16-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

HIP6521CBZA-T

功能描述:IC REG QD BCK/LINEAR 16-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

HIP6521CBZ-T

功能描述:电压模式 PWM 控制器 4 IN 1 PWM/LINEAR CNTRLR 5V RoHS:否 制造商:Texas Instruments 输出端数量:1 拓扑结构:Buck 输出电压:34 V 输出电流: 开关频率: 工作电源电压:4.5 V to 5.5 V 电源电流:600 uA 最大工作温度:+ 125 C 最小工作温度:- 40 C 封装 / 箱体:WSON-8 封装:Reel

HIP6521EVAL1

功能描述:电源管理IC开发工具 HIP6521 PWM & TRPL L LINEAR CNT EVAL BRD

RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V

HIP6601

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Synchronous-Rectified Buck MOSFET Drivers

HIP6601_04

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Synchronous-Rectified Buck MOSFET Drivers

HIP6601A

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Synchronous Rectified Buck MOSFET Drivers